International Journal of Electrical and Electronics Engineering (IJEEE) ISSN 2278-9944 Vol. 2, Issue 3, July 2013, 19-24 © IASET

# A HIGH CMRR, LOW-POWER OPERATIONAL TRANSCONDUCTANCE AMPLIFIER WITH 0.18μM CMOS TECHNOLOGY

## BHUPENDRA BANJARE, D. S. AJNAR & P. K. JAIN

Department of Electronics & Instrumentation Engineering, Shri G. S. Institute of Technology and Science, Indore, Madhya Pradesh, India

#### ABSTRACT

This paper represent an Operational Transconductance Amplifier (OTA) which is a basic building block in many analog circuit such as in data converter's (ADC &DAC), biquad filter design and instrumentation amplifiers. This OTA is implemented using 0.18 $\mu$ m CMOS technology with cadence environment and it has  $\pm 1.25v$  power supply with biasing current of 33nA. OTA has been simulated with virtuoso simulator and simulation results are measured. Post layout simulations for a 1 pF load capacitance shows that OTA achieves a gain bandwidth of 270 KHz at a phase margin  $68.43^{\circ}$  with 90.27 dB DC gain. This OTA is having CMRR of 154 dB, PSRR of 119 dB, Power dissipation of 29.58nW and Slew Rate 2.49 V/ $\mu$ sec.

**KEYWORDS:** Cadence, Operational Transconductance Amplifier (OTA), CMRR, PSRR, DC Gain, Unity Gain Bandwidth (UGBW), CMFB

# INTRODUCTION

The operational amplifiers (OPAMP) are basic building blocks in implementing a variety of analog Circuits such as amplifiers, filters, integrators, differentiators, summers, oscillators etc. For higher frequencies, however, OPAMP designs become difficult due to their frequency limit [2], [3]. At those high frequencies, operational transconductance amplifiers (OTAs) are deemed to be promising to replace OPAMPS as the building blocks [1]-[11].

Fully differential OTAs are preferred because they provide larger signal swing, better distortion performance, better CM noise and supply noise rejection. The Fully differential OTAs require a common-mode feedback (CMFB) circuit.

In Reference [4] a CMFB circuit which operated at 0.5 V by using two resistors to sense the output CM levels was designed. But this structure increases the die area and reduces the gain due to longer loads the OTA. To overcome some of these problems, a CMFB circuit has been reported [5].

This structure uses of four PMOS and two NMOS transistors. The NMOS devices is a bulk-input current mirror, which compares the current of the PMOS devices and then difference of these current is fed to the gate of the input transistors for controlling of the output CM voltages. This paper is given a novel continuous-time CMFB circuit that is able to operate with an ultra low-voltage supply.

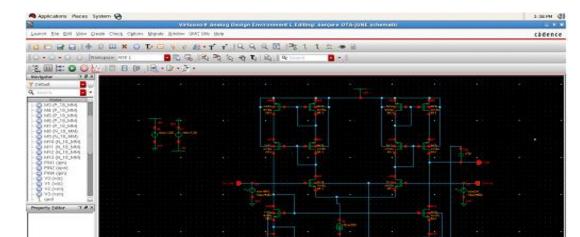

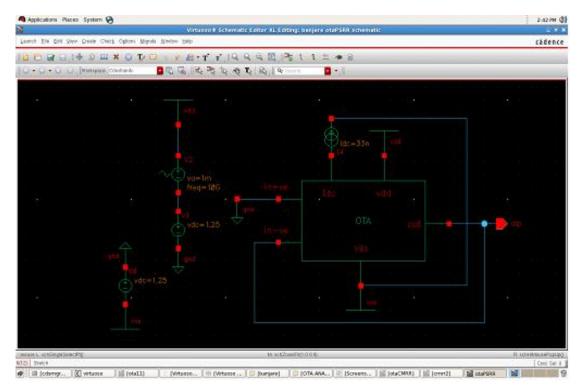

So there are several different OTA's are used in which this OTA (shown in figure 1) is a simple OTA with low supply voltage of VDD=+1.25V and VSS=-1.25V and high gain. The design parameters of this OTA are shown in below table 1.

## OPERATIONAL TRANSCONDUCTANCE AMPLIFIER (OTA)

Figure 1: Schematic of OTA

**Table 1: Dimensions of CMOS Transistors**

| Transistor Type | Transistor Name                | W(µm) | L(µm) |

|-----------------|--------------------------------|-------|-------|

| PMOS            | M0, M1, M2, M3, M4, M5, M6, M7 | 4     | 1     |

| NMOS            | M8, M9, M10, M11, M12, M13     | 2     | 1     |

## SIMULATION RESULTS OF PROPOSED OTA

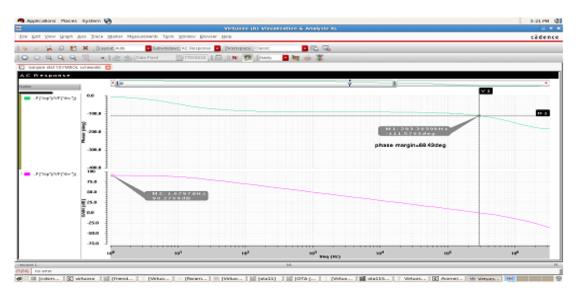

The design of this OTA is done using Cadence Tool. The simulations were performed under normal condition (room temperature) on Cadence Spectre Environment using UMC 0.18  $\mu$ m CMOS technology with  $\pm 1.25 v$  power supply. The AC simulation results are shown in Figure 2. It shows that the dc gain is 90.27 dB and the bandwidth is 270 KHz. The phase margin is about 68.43°. Furthermore, Table II summarizes the simulated performance of this OTA.

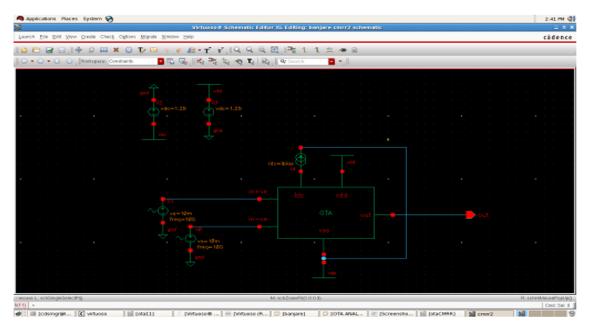

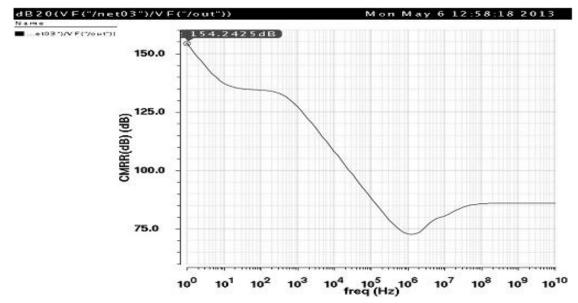

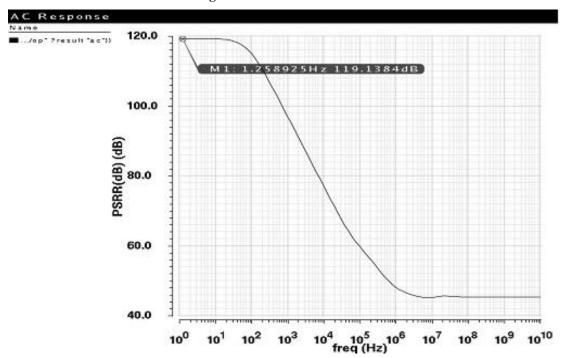

Figure 3 shows schematic for CMRR analysis of OTA. The change in CMRR with frequency is shown in figure 4 which is 154 dB. Figure 5 shows schematic for PSRR analysis. The variation in PSRR is shown in figure 6 which is 119 dB.

Figure 2: AC Response of OTA

|  | Table 2: Si | pecifications | of Proposed | OTA | Compared | with | Similar | Works |

|--|-------------|---------------|-------------|-----|----------|------|---------|-------|

|--|-------------|---------------|-------------|-----|----------|------|---------|-------|

| Specification     | [4]     | [5]     | This Design |

|-------------------|---------|---------|-------------|

| Technology        | 0.18-µm | 0.18-µm | 0.18-µm     |

| Technology        | CMOS    | CMOS    | CMOS        |

| Supply voltage    | 0.5v    | 0.5v    | ±1.25v      |

| Open-loop DC Gain | 62 dB   | 65 dB   | 90.27 dB    |

| Phase margin      | 60°     | 65°     | 68.43°      |

| Gain margin       | NA      | NA      | 30 dB       |

| Load Capacitors   | 20 pf   | 20 pf   | 1 pf        |

| Power Consumption | 110 μW  | 28 μW   | 29.58nW     |

| Unity Gain BW     | 10 MHz  | 550 KHz | 270 KHz     |

| CMRR              | NA      | NA      | 154 dB      |

| PSRR              | NA      | NA      | 119 dB      |

| Slew Rate         | NA      | NA      | 2.49v/µsec  |

NA. Not Available

# **COMMON MODE REJECTION RATIO (CMRR)**

Figure 3: Schematic for CMRR

Figure 4: CMRR versus Frequency

# POWER SUPPLY REJECTION RATIO (PSRR)

Figure 5: Schematic for PSRR

Figure 6: PSRR versus Frequency

## **CONCLUSIONS**

In this paper a simple OTA configuration for low-voltage and low-power application in 0.18 µm CMOS process has been presented. A complete analysis of this OTA is presented in this paper which shows how this circuit leads to a high gain and high CMRR. With the load capacitor of 1 pF, the design demonstrates a dc Gain of 90.27 dB with a bandwidth of 270 KHz and high CMRR of 154 dB. So this work can be used in process controller, physical transducers and small battery operated devices, continuous-time filter design, and ADC design and instrumentation amplifiers.

## **ACKNOWLEDGEMENTS**

This work has been carried out in SMDP VLSI laboratory of the Electronics and Instrumentation Engineering Department of Shri G S Institute of Technology and Science, Indore, India. This SMDP VLSI project is funded by Ministry of Information and Communication Technology, Government of India. Authors are thankful to the Ministry for facilities provided under this project.

#### REFERENCES

- 1. J. H. Botma, R.F. Wassenaar, R. J. Wiegerink, "A low voltage CMOS Op Amp with a rail-to-rail constant-gm input stage and a class AB rail-to-rail output stage", IEEE 1993 ISCAS, Chicago, pp.1314-1317.

- You Zheng and Carlos E. Saavedra, "Feed forward-Regulated Cascode OTA for Gigahertz Applications", IEEE Transactions on Circuits and Systems, 2008

- 3. Anil Kavala, Kondekar P. N, and Yang Sun, "A low voltage, low power linear pseudo Differential OTA for ultrahigh frequency applications", IEEE, International workshop on Antenna Technology, 2009.

- 4. S. Chatterjee, Y. Tsvidis and P. Kinget, "0.5 V Analog Circuit Techniques and Their Application to OTA and Filter Design," IEEE Journal of Solid State circuits, Vol. 40, No. 12, 2005, pp. 2373-2387. doi:10.1109/JSSC.2005.856280

- M. Trakimas and S. Sonkusale, "A 0.5 V Bulk-Input OTA with Improved Common-Mode Feedback for Low-Frequency Filtering Applications," Analog Integrated Circuits and Signal Processing, Springer Press, New York, 2009, pp. 83-89.

- 6. Slawomir Koziel, Stanislaw Szczepanski, "Design of Highly Linear Tunable CMOS OTA For-continuous Time Filters," *IEEE TransCircuits Syst.*, vol. 49, no. 2, Feb. 2002

- 7. Tien-Yu Lo, Chung-Chih Hung, "A 1-V 50-MHz Pseudo-differential OTA with Compensation of The Mobility Reduction," *IEEE Trans Circuits Syst.*, vol. 54, no. 12, Dec. 2007

- 8. Zhenhua Wang, Walter Guggenbuhl, "A Voltage-Controllable Linear MOS Transconductor Using Bias Offset Technique," *IEEE J. Solid- State Circuits*, vol. 25, no. 1, Feb. 1990

- 9. Stanislaw Szczepanski, Jacek Jakusz, Rolf Schaumann, "A Linear Fully Balanced CMOS OTA For VHF Filtering Applications," *IEEE Trans Circuits Syst.*, vol. 44, no. 3, Mar. 1997

- 10. Ahmed Nader Mohieldin, Edgar Sanchez-Sinencio, Jose Silva-Martinez, "Nonlinear Effects in Pseudo Differential OTAs with CMFB," *IEEE Trans Circuits Syst.*, vol. 50, no. 10, Oct. 2003

- 11. I. S. Han, "A novel tunable transconductance amplifier based on voltage-controlled resistance by MOS transistors," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 53, no. 8, pp. 662–666, Aug. 2006.